# PE Refresher Course

# **Digital Systems and Computers**

Joanne Degroat

degroat.1@osu.edu

ece.osu.edu/~degroat

PE Refresher Computer Area -Joanne DeGroat

1

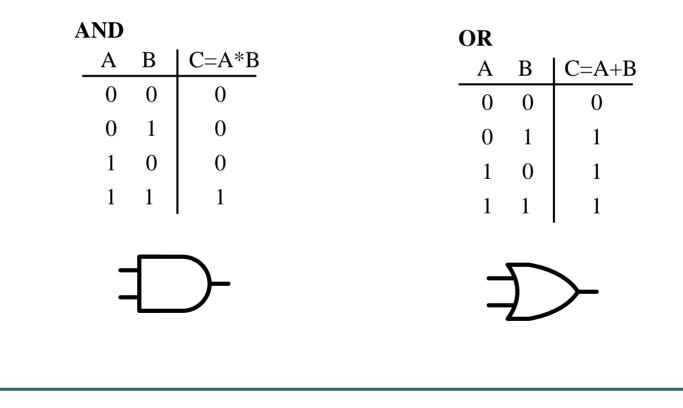

#### The Basics

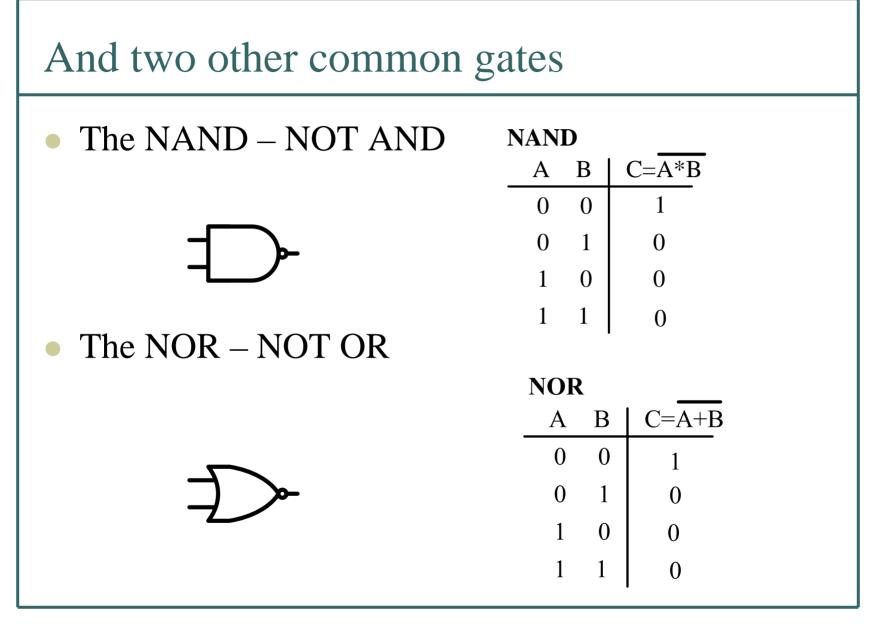

#### • Basic Switching Algebra

Truth Tables of Basic Functions AND and OR

#### The Basics (cont)

Inversion – The not or inverter gate

• Exclusive OR - XOR

**NOT** - inversion

| А | A |

|---|---|

| 0 | 1 |

| 1 | 0 |

**XOR** - exclusive OR

| Α | В | $X=A \oplus B$ |

|---|---|----------------|

| 0 | 0 | 0              |

| 0 | 1 | 1              |

| 1 | 0 | 1              |

| 1 | 1 | 0              |

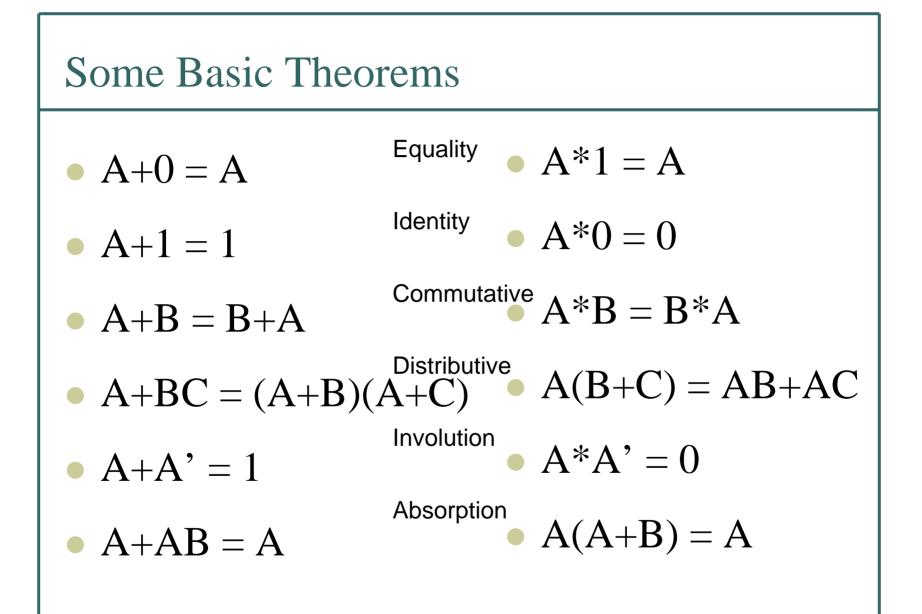

#### More Theorems

- A+AB = A + B A(A + B) = AB

- $\overline{(A + B)} = AB$   $\overline{(AB)} = \overline{A} + \overline{B}$ • A \* A = A A + A = ADeMorgan's Law

- (A) = A

- $AB + \overline{A}C + BC = AB + \overline{A}C$

- Dual: (A+B)(A+C)(B+C) = (A+B)(A+C)

#### Truth Tables

Truth tables can be used to prove equalities

| <b>Proof of DeMorgan's Law</b> |   |     |                    |     |   |                             |  |  |  |  |

|--------------------------------|---|-----|--------------------|-----|---|-----------------------------|--|--|--|--|

| Α                              | В | A+B | $\overline{(A+B)}$ | Ā   | B | $\overline{A}*\overline{B}$ |  |  |  |  |

| 0                              | 0 | 0   | 1                  | 1   | 1 | 1                           |  |  |  |  |

| 0                              | 1 | 1   | 0                  | 1   | 0 | 0                           |  |  |  |  |

| 1                              | 0 | 1   | 0                  | 0   | 1 | 0                           |  |  |  |  |

| 1                              | 1 | 1   | 0                  | 0   | 0 | 0                           |  |  |  |  |

|                                |   |     |                    | _ = |   |                             |  |  |  |  |

|                                |   |     |                    |     |   |                             |  |  |  |  |

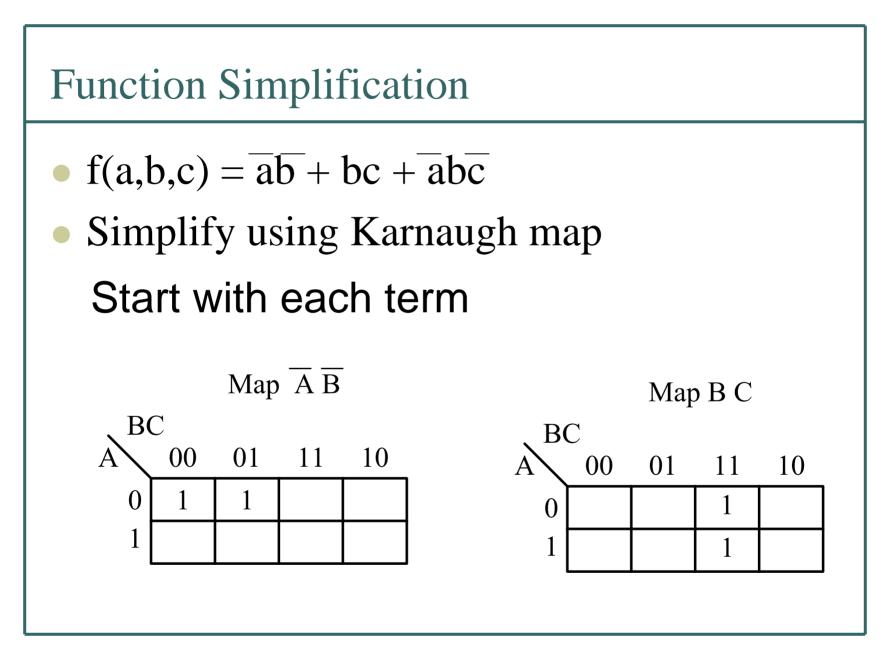

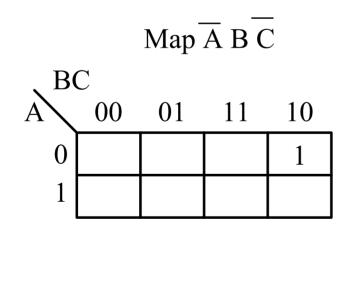

**Function Simplification**

•

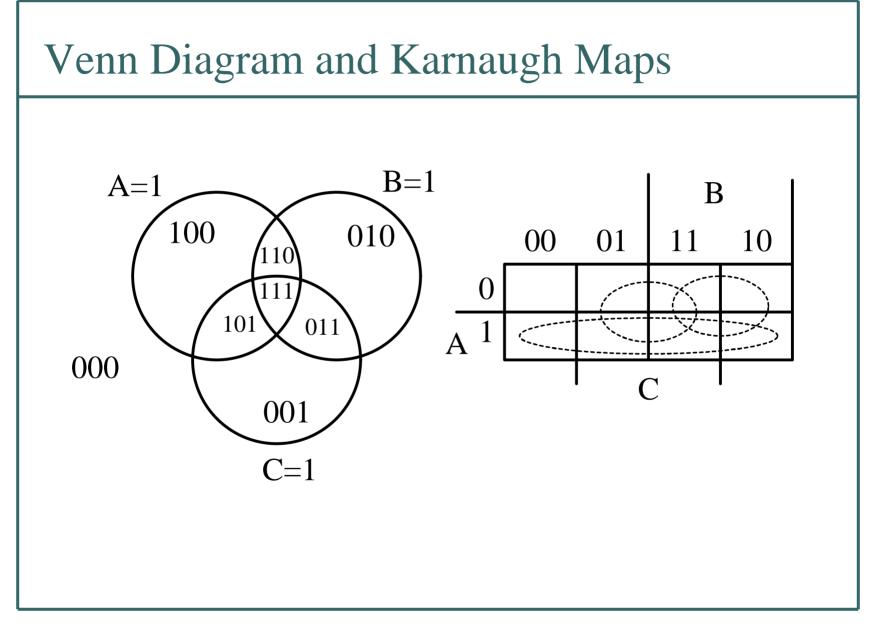

$$f(a,b,c) = \overline{ab} + bc + \overline{a}b\overline{c}$$

A term with a Single element results In 4 ones A term with 2 elements Gives two A term with 3 elements Gives a single 1

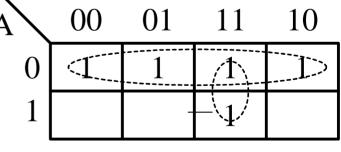

# Simplify K maps

- Conbining the previous three maps

- Can represent what a K map shows by a sum of products

- Take the largest group possible

- On one line, a square, two BC

- Group needs to be a

- power of 2

$f(a,b,c) = \overline{a} + bc$

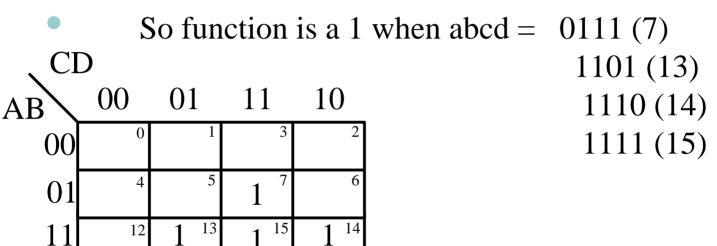

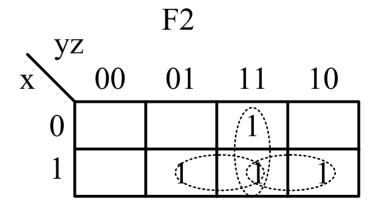

## 4 variable functions

• Also expressed in minterm notation

•

$$f(a,b,c,d) = \Sigma m(7,13,14,15)$$

9

П

8

10

10

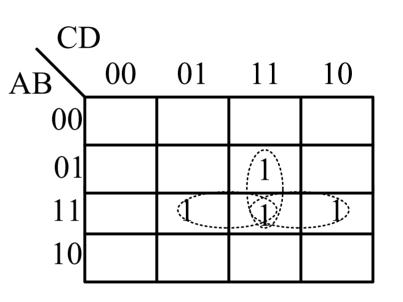

#### Form into largest groups

- For 4 variables form into groups of

- 16 function would be a

0 or a 1

- 8 1 variable

- 4 2 variables

- 2 3 variables

- Simplifies to

- F = ABD + BCD + ABC

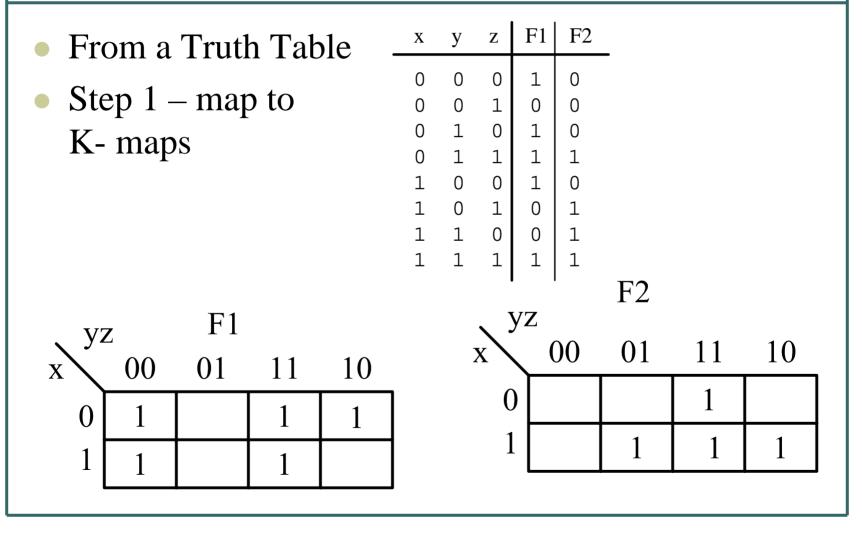

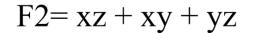

# Another Example of function simplification

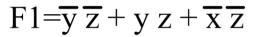

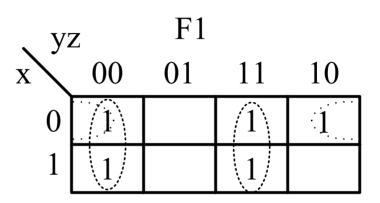

# Step 2 – Generate simplified equation

• For F1

• For f2

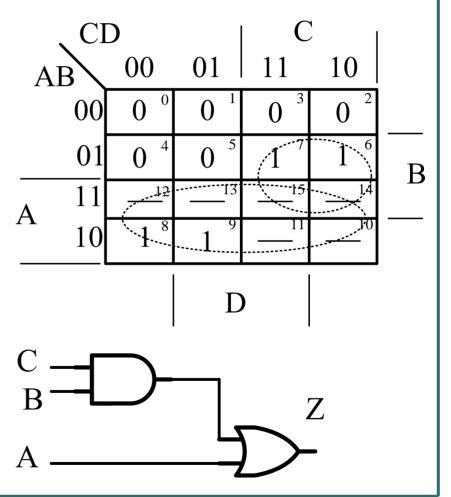

#### Example Problem

- Design a circuit having 1 output Z and 4 inputs A B C D which represents a BCD number, such that Z = 1 if the BCD number is greater than 5.

- BCD stands for binary coded decimal

- Takes 4 binary digits

- Only 0 through 9 are used

# Map onto K map

- Fill in a 1 whenever output should be a 1

- Here that would be 6, 7, 8 or 9

- And a 0 for blocks 0 through 5

# The K map cont

- Filled in

- What should other blocks be?

- They would be don't cares as in BCD notation they will never occur

- And final K map for simplification is

## Simplified using don't cares

- Form the largest power of 2 grouping from 1's and don't cares

- Cover all the 1's but don't need to cover all the don't cares

- Get Z = A + BC

- Gate implementation

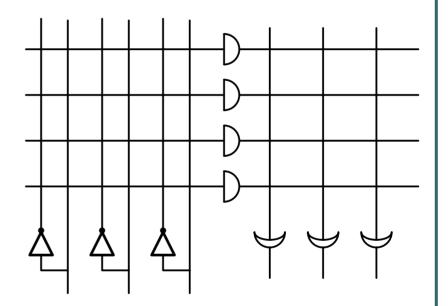

### PLAs

- PLA Programmable Logic Array

- PAL Programmable Array Logic – much like a PLA but restricted connections

- Formed of an AND plane and an OR plane

### PLAs

- PLA Programmable Logic Array

- PAL Programmable Array Logic – much like a PLA but restricted connections

- Formed of an AND plane and an OR plane

## PLA example

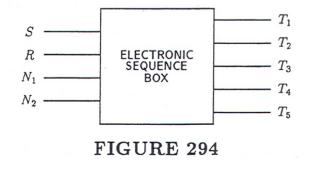

Problem: A sequence box to control automatic starting of a jet engine is to be designed. It has the following signals

• Problem stated on next slide.

#### Problem statement

#### XX

#### SITUATION:

An electronic sequence box to control the starting of a turbojet engine is shown in Figure 294 below. Table 294 lists the combinations and was developed in accordance with the engine manufacturer's specifications. Combinations which are not listed cannot occur. The inputs and outputs of the electronic sequence box are:

- S (Start and idle switch)

- $N_1$  (Cranking speed switch)

- $T_1$  (Air Solenoid Valves, Igniter)

- $T_3$  (Fuel Metering Valve Actuator OFF)

- $T_5$  (Fuel Metering Valve Actuator IDLE)

- R (Run)

- $N_2$  (Self-sustaining speed switch)

- T<sub>2</sub> (Fuel Supply Valve Solenoid)

- T<sub>4</sub> (Fuel Metering Valve Actuator RUN)

#### **REQUIREMENTS:**

A reasonably simple solid-state logic implementation of the electronic sequence box is desired.

- (a) Derive minimal combinational logic equations and show implementation using standard logic elements.

- (b) Prepare a PLA (progammable logic array) table that satifies the table of combinations.

#### Problem statement translated to a table

#### • The table

| SEQUENCE                        | S | R | $N_1$ | $N_2$ | $T_1$ | $T_2$ | $T_3$ | $T_4$ | $T_5$ |     |

|---------------------------------|---|---|-------|-------|-------|-------|-------|-------|-------|-----|

| MASTER SWITCH<br>"OFF"          | 0 | 0 | 0     | 0     | 0     | 0     | 1     | 0     | 0     |     |

| MASTER SWITCH<br>set to "START" | 1 | 0 | 0     | 0     | 1     | 0     | 0     | . 0   | 0     | · . |

| Cranking Speed<br>reached       | 1 | 0 | 1     | 0     | 1     | 1     | 0     | 0     | 1     |     |

| Self-sustained speed reached    | 1 | 0 | 1     | 1     | 0     | 1     | 0     | 0     | 1     |     |

| MASTER SWITCH<br>set to "RUN"   | 0 | 1 | 1     | 1     | 0     | 1     | 0     | 1     | 0     |     |

| MASTER SWITCH<br>turned "OFF"   | 0 | 0 | 1     | 1     | 0     | 1     | 1     | 0     | 0     |     |

| Engine Speed falls below $N_2$  | 0 | 0 | 1     | 0     | 0     | 0     | 1     | 0     | 0     |     |

TABLE 294

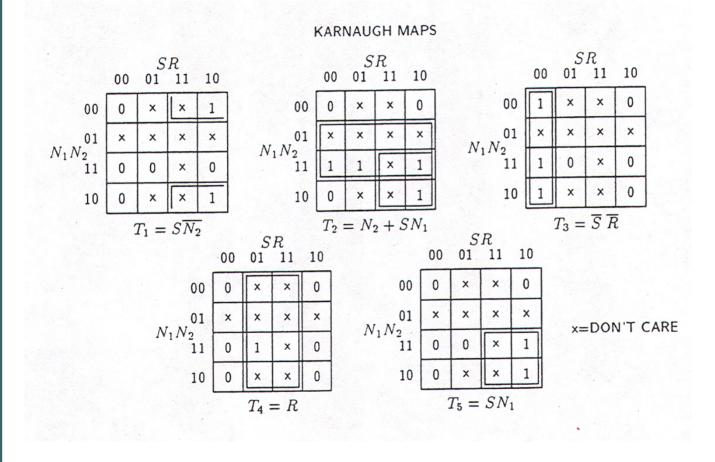

#### K maps for the sequencer

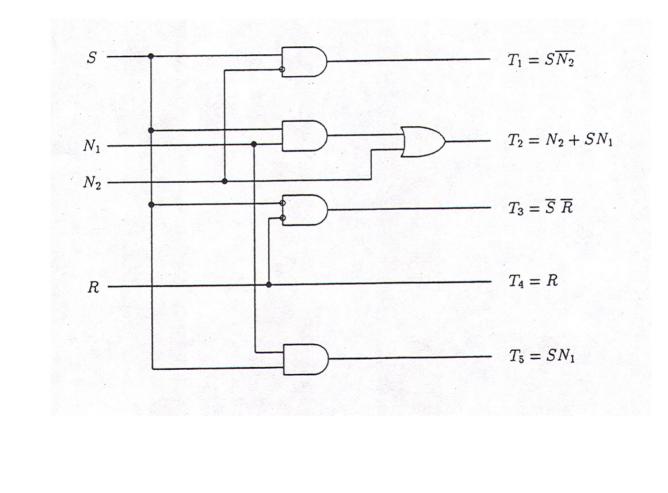

## The logic implementation in gates

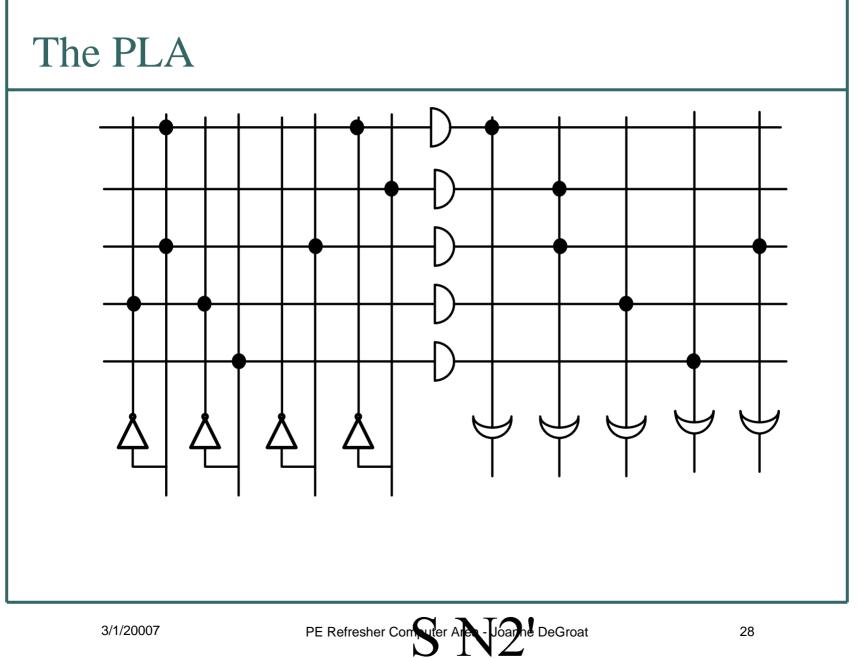

#### And a PLA implementation

• You will most like be asked for this in a table representation form like this

| PRODUCT                     |   |  | INPUTS |   |       |       | OUTPUTS |       |       |       |       |  |

|-----------------------------|---|--|--------|---|-------|-------|---------|-------|-------|-------|-------|--|

| TERM                        |   |  | S      | R | $N_1$ | $N_2$ | $T_1$   | $T_2$ | $T_3$ | $T_4$ | $T_5$ |  |

| $S\overline{N_2}$           | 1 |  | 1      | - | -     | 0     | 1       | -     | -     | -     | -     |  |

| $N_2$                       | 2 |  | -      | - | -     | 1     | -       | 1     | -     | -     | -     |  |

| $SN_1$                      | 3 |  | 1      | - | 1     | -     | -       | 1     | -     | -     | 1     |  |

| $\overline{S} \overline{R}$ | 4 |  | 0      | 0 | -     | -     | -       | -     | 1     | -     | -     |  |

| R                           | 5 |  | -      | 1 | -     | -     | -       | -     | -     | 1     | -     |  |

PROGRAM LOGIC ARRAY (PLA) - PLA TABLE

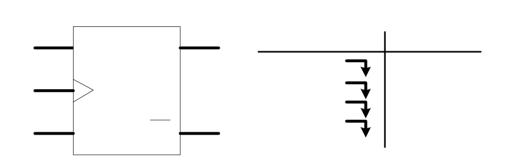

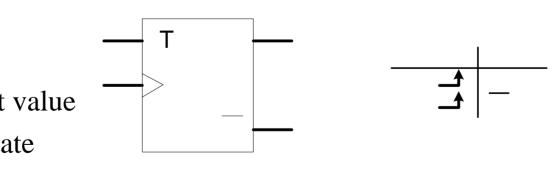

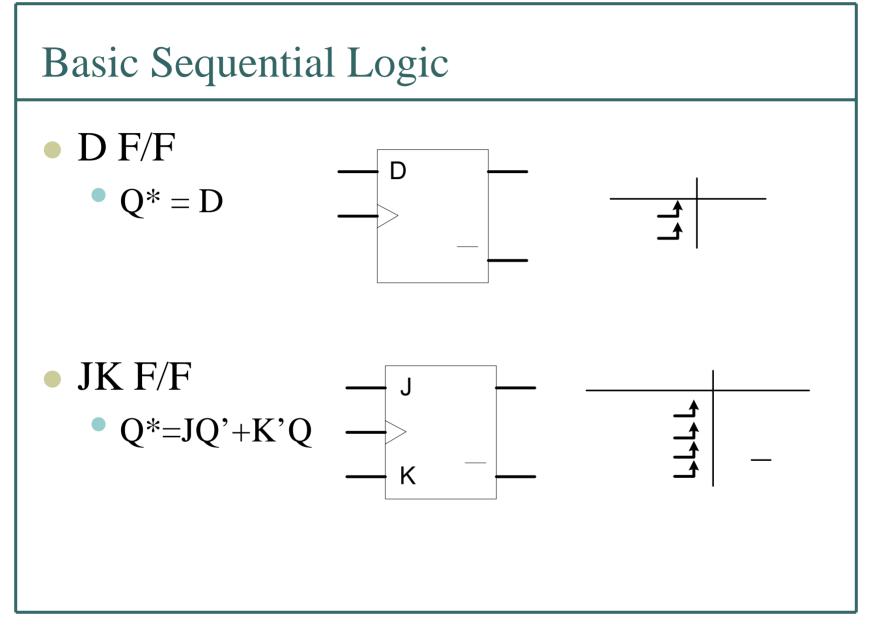

# Basic Sequential Logic

- Flip Flops

- Set Reset FF

- Q\*=S+R'Q

- Toggle FF

- Q\*=Q'

• Or next state

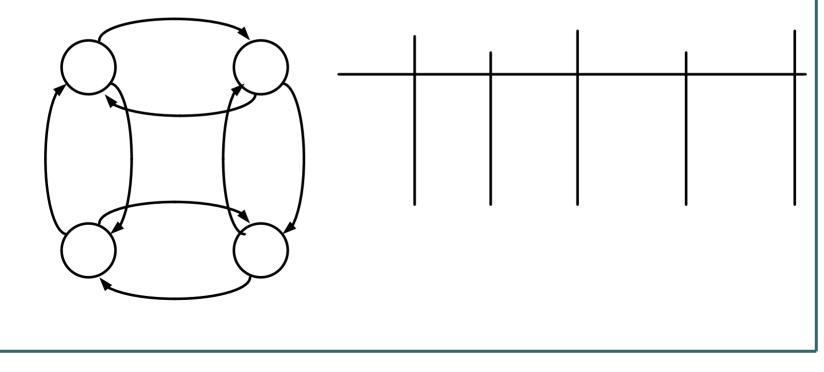

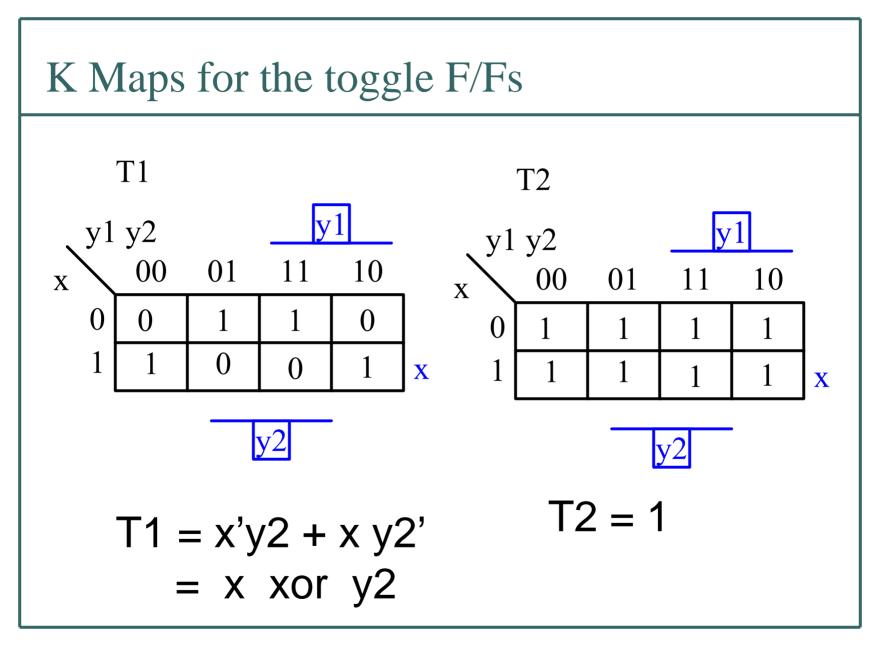

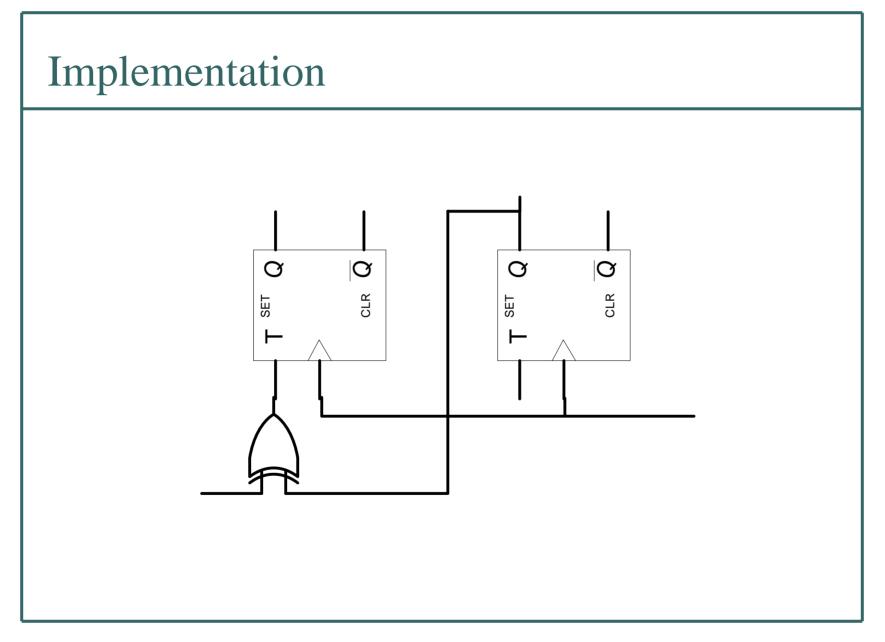

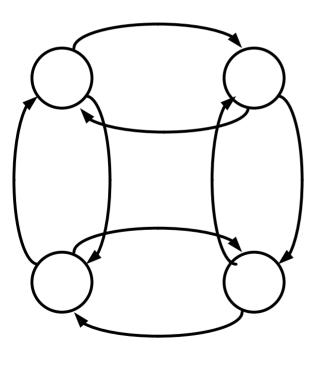

# A Simple up/down counter

• Start with a state diagram

# A Simple up/down counter

- Start with a state diagram

- And a state table for T F/Fs